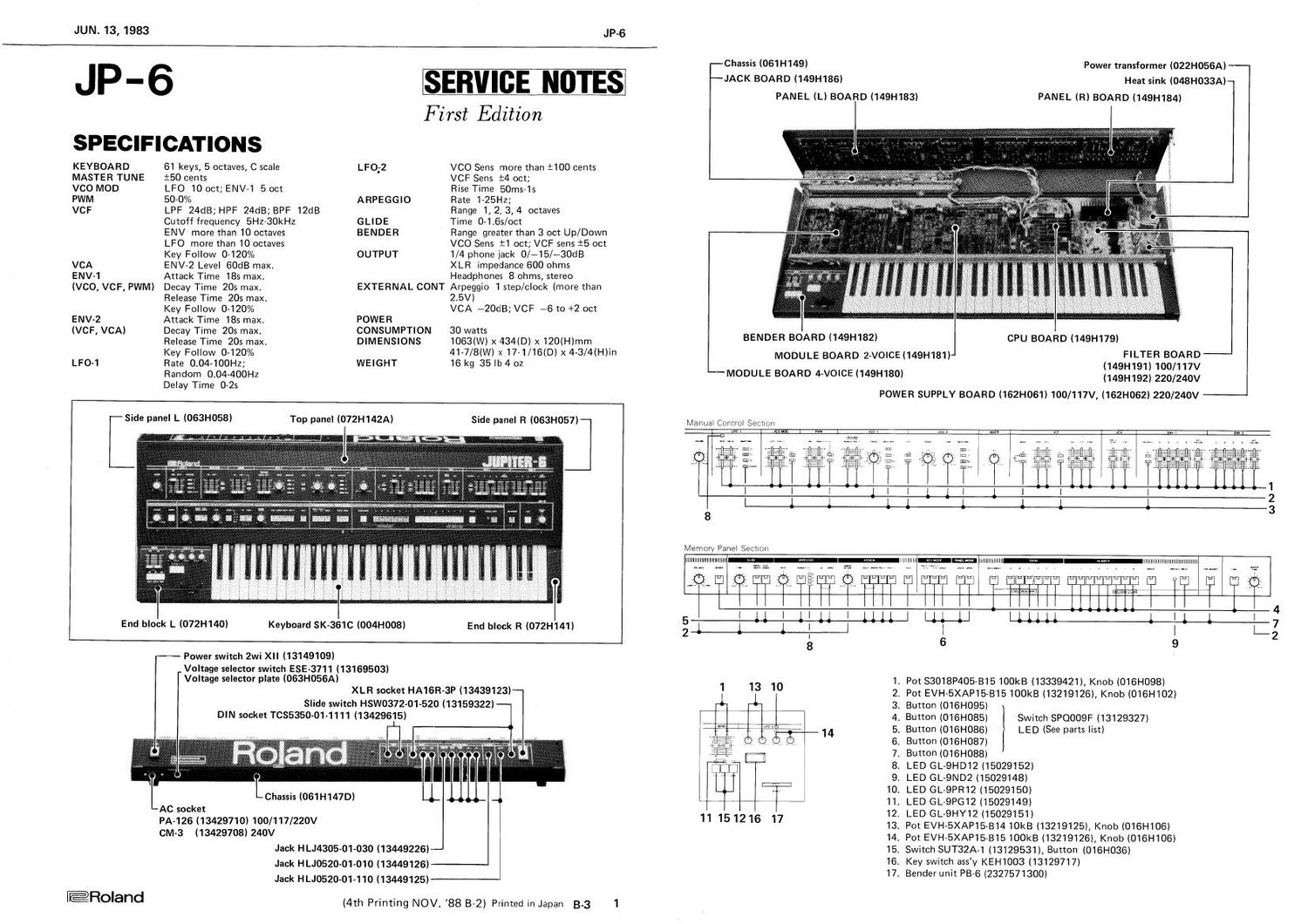

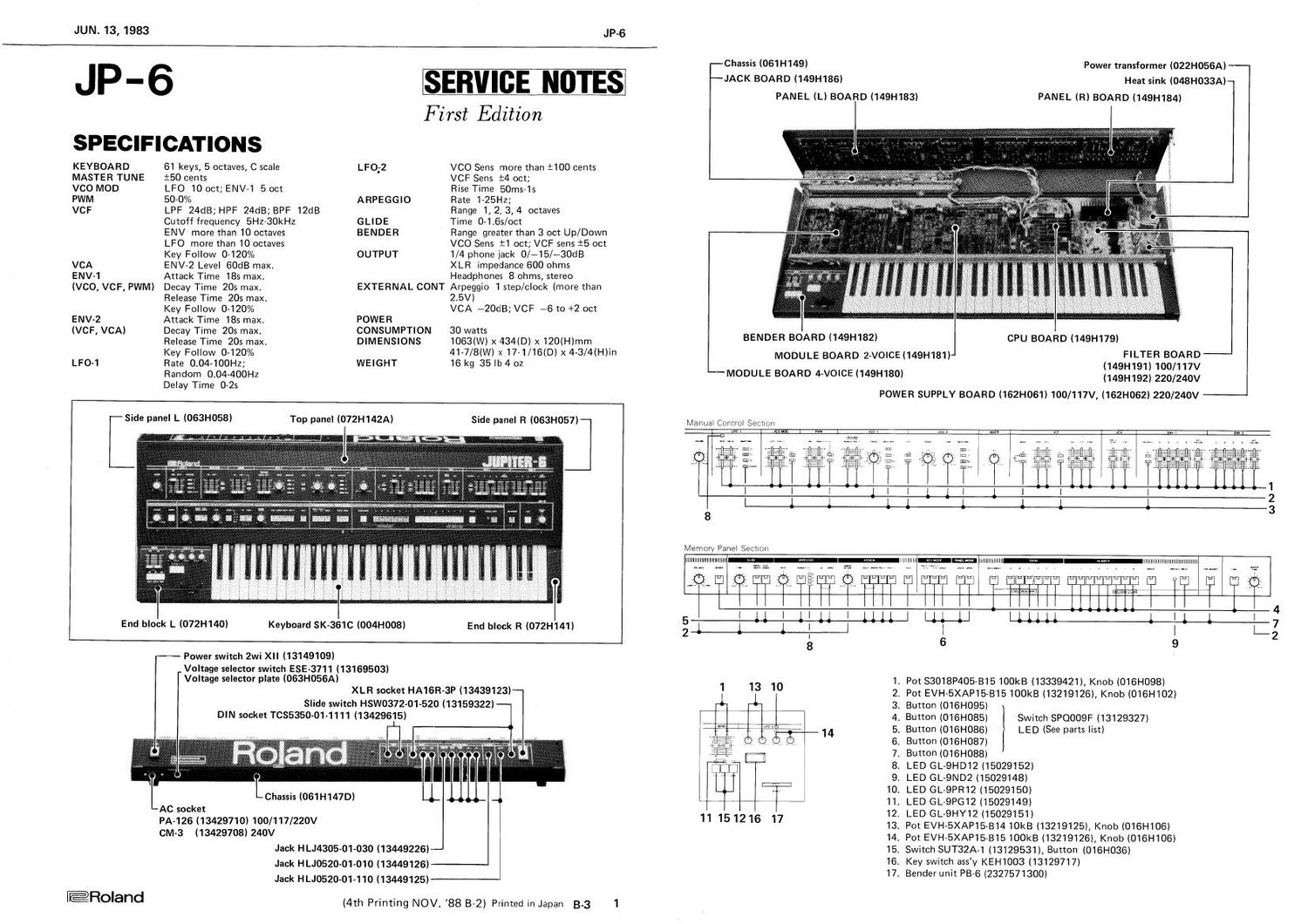

ROLAND JP 6

This is the 27 pages manual for ROLAND JP 6.

Read or download the pdf for free. If you want to contribute, please upload pdfs to audioservicemanuals.wetransfer.com.

Page: 1 / 27

This is the 27 pages manual for ROLAND JP 6.

Read or download the pdf for free. If you want to contribute, please upload pdfs to audioservicemanuals.wetransfer.com.