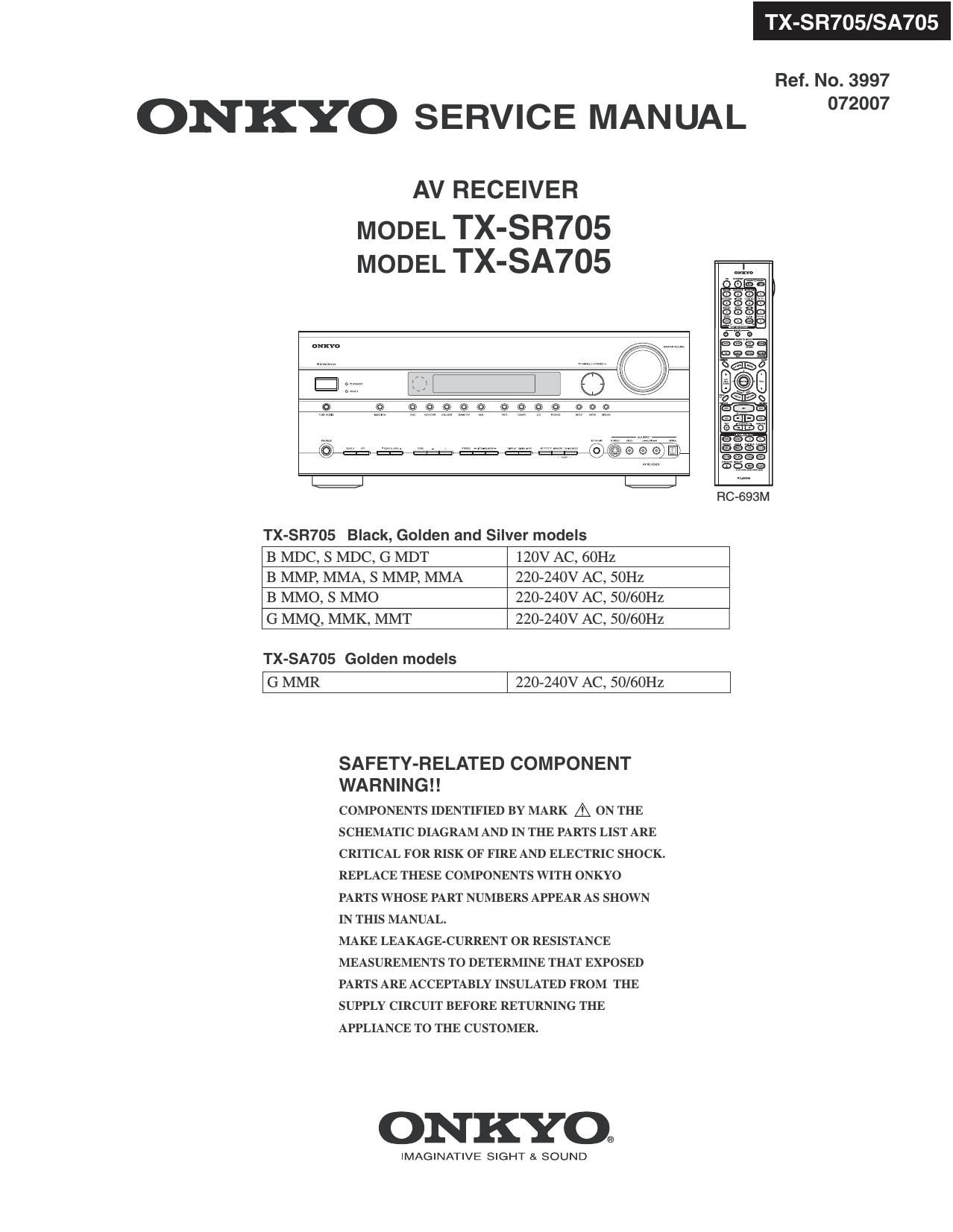

Onkyo TXSR 705 Service Manual

This is the 199 pages manual for Onkyo TXSR 705 Service Manual.

Read or download the pdf for free. If you want to contribute, please upload pdfs to audioservicemanuals.wetransfer.com.

Page: 1 / 199